2.1 Verilog 基础语法

格式 Verilog 是区分大小写的。 格式自由,可以在一行内编写,也可跨多行编写。 每个语句必须以分号为结束符。空白符(换行、制表、空格)...

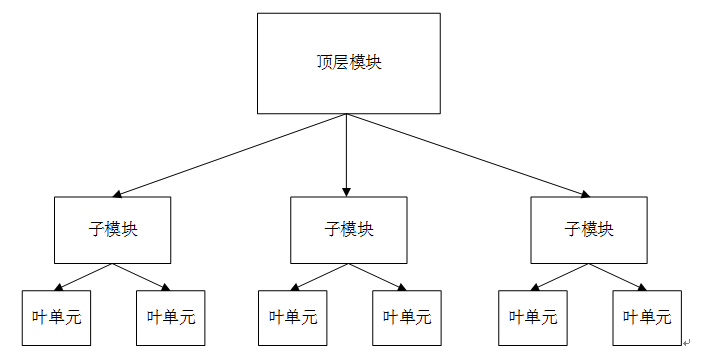

1.4 Verilog 设计方法

设计方法 Verilog 的设计多采用自上而下的设计方法(top-down)。即先定义顶层模块功能,进而分析要构成顶层模块的必要子模块;然后进一步对...

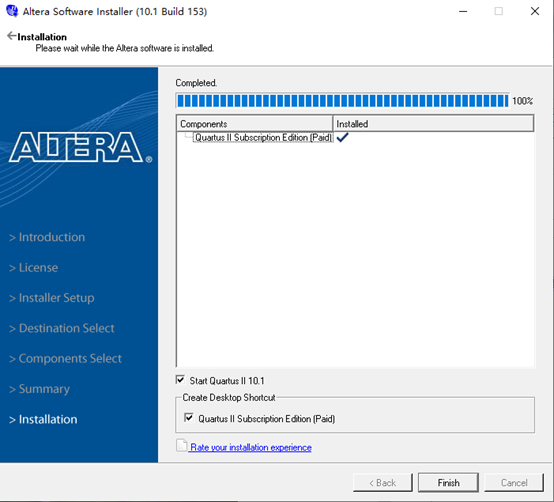

1.3 Verilog 环境搭建

学习 Verilog 做仿真时,可选择不同仿真环境。FPGA 开发环境有 Xilinx 公司的 ISE(目前已停止更新),VIVADO;因特尔公司的 Quartus II;ASIC...

1.2 Verilog 简介

Verilog 具有很强的电路描述与建模能力,能从多个层次对数字系统进行描述和建模。因此,在简化硬件设计任务、提高设计效率与可靠性、语言易读...

1.1 Verilog 教程

Verilog HDL(简称 Verilog )是一种硬件描述语言,用于数字电路的系统设计。可对算法级、门级、开关级等多种抽象设计层次进行建模。 Verilog...

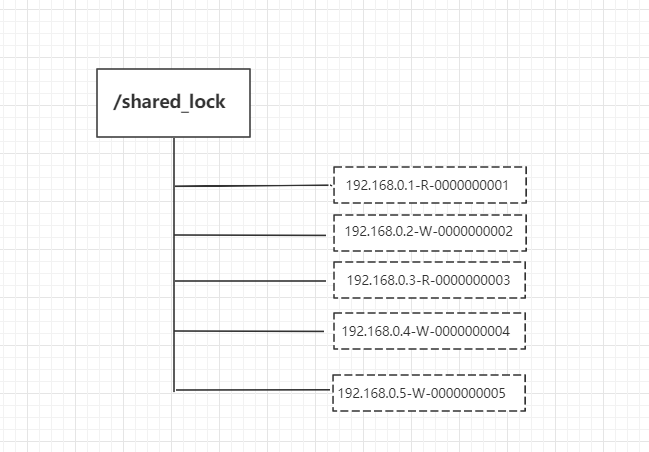

14.0 Zookeeper 分布式锁实现原理

分布式锁是控制分布式系统之间同步访问共享资源的一种方式。下面介绍 zookeeper 如何实现分布式锁,讲解排他锁和共享锁两类分布式锁。 排他...

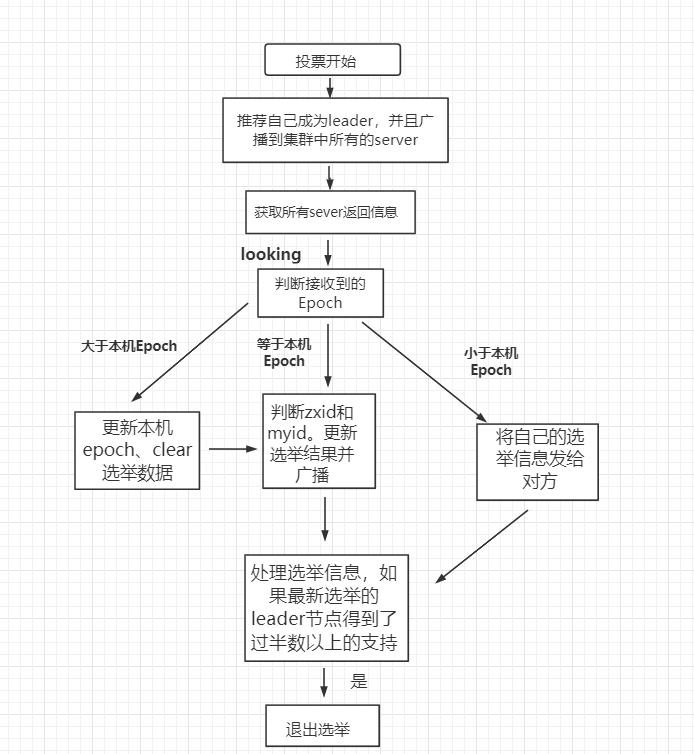

13.0 Zookeeper Leader 选举原理

zookeeper 的 leader 选举存在两个阶段,一个是服务器启动时 leader 选举,另一个是运行过程中 leader 服务器宕机。在分析选举原理前,先介绍...

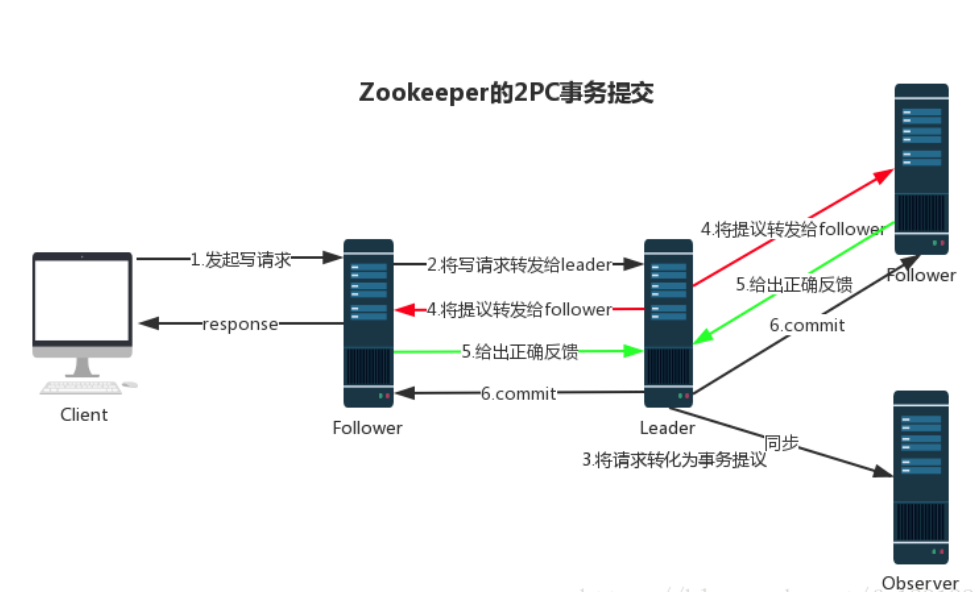

12.0 Zookeeper 数据同步流程

在 Zookeeper 中,主要依赖 ZAB 协议来实现分布式数据一致性。 ZAB 协议分为两部分: 消息广播 崩溃恢复 消息广播 Zookeeper 使用单...

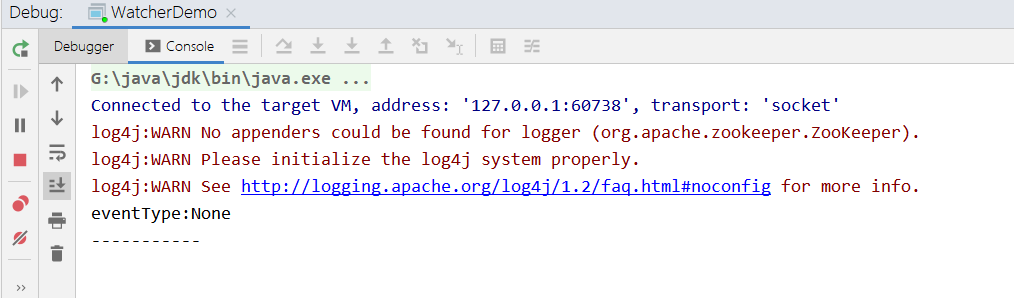

11.0 Zookeeper watcher 事件机制原理剖析

zookeeper 的 watcher 机制,可以分为四个过程: 客户端注册 watcher。 服务端处理 watcher。 服务端触发 watcher 事件。 客户端回调 wa...

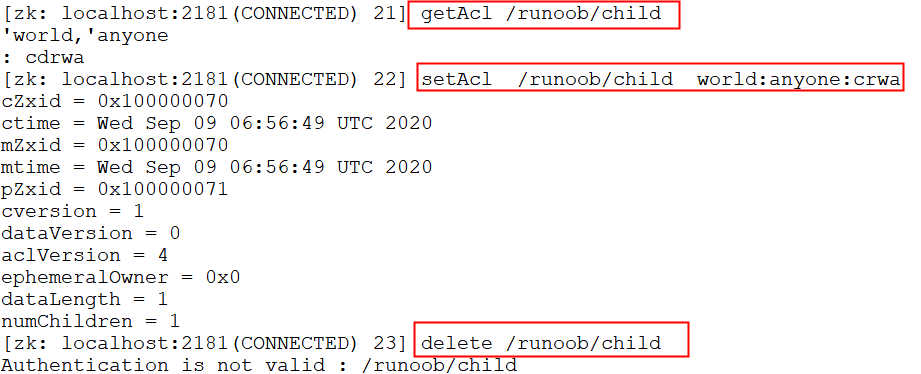

10.0 Zookeeper 权限控制 ACL

zookeeper 的 ACL(Access Control List,访问控制表)权限在生产环境是特别重要的,所以本章节特别介绍一下。ACL 权限可以针对节点设置相关读...