本教程经常有提及综合这个词语。或者说有些逻辑不能综合成实际电路,或者说有些逻辑设计综合后的电路会有一些安全隐患。本章就简单介绍下逻辑综合的相关知识,仅从理论层次和普遍认知的角度来阐述。待那个懵懂求知少年变成中年秃顶大叔,再来介绍逻辑综合的具体实践。好像也没有多少时日了(手动狗头)。

基本概念

综合,就是在标准单元库和特定的设计约束基础上,把数字设计的高层次描述转换为优化的门级网表的过程。标准单元库对应工艺库,可以包含简单的与门、非门等基本逻辑门单元,也可以包含特殊的宏单元,例如乘法器、特殊的时钟触发器等。设计约束一般包括时序、负载、面积、功耗等方面的约束。

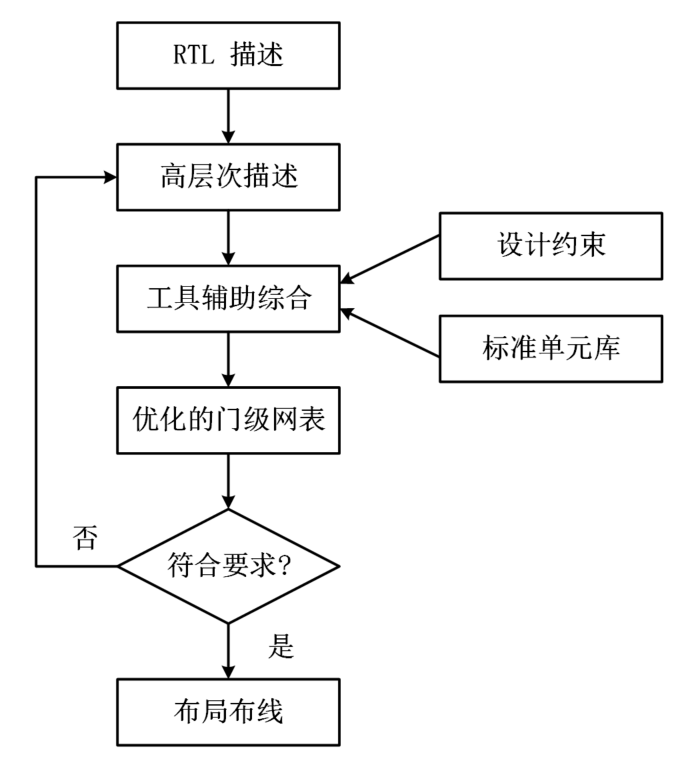

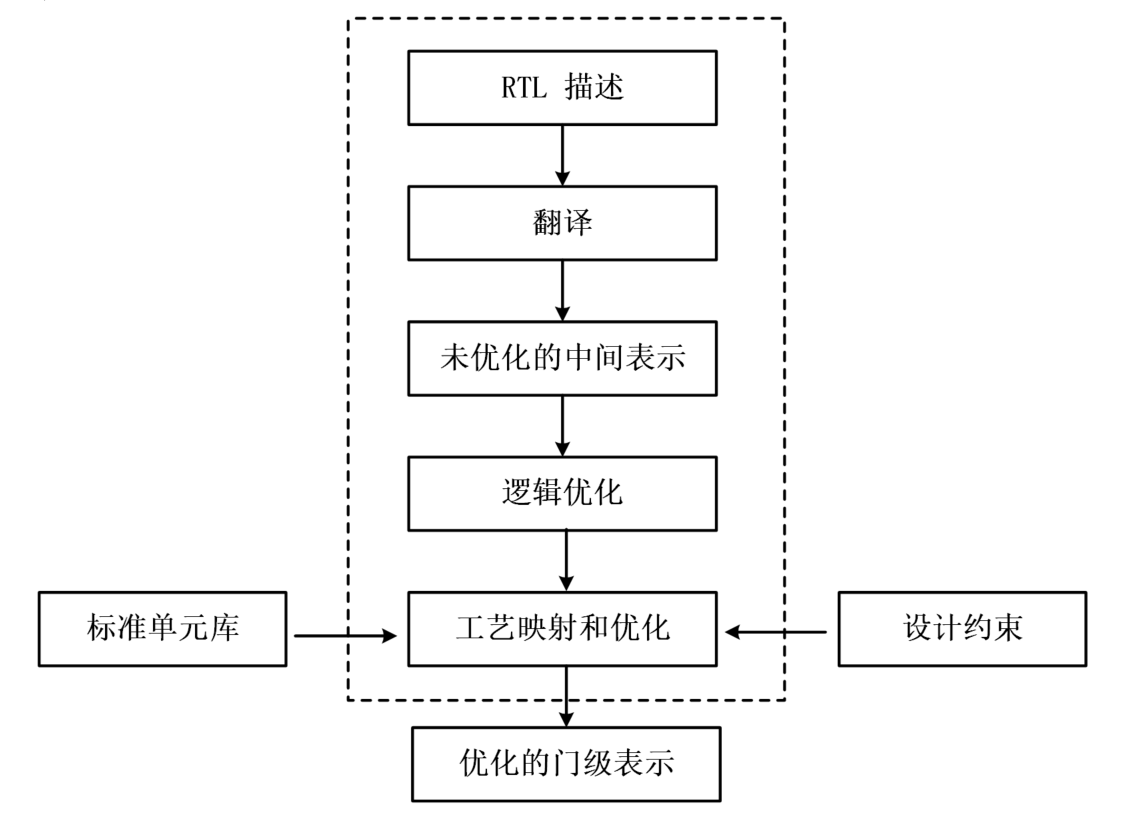

无论是数字芯片设计,还是 FPGA 开发,现在综合过程基本都是借用计算机辅助逻辑综合工具,自动的将高层次描述转换为逻辑门电路。设计人员可以将精力集中在系统结构方案、高层次描述、设计约束和标准工艺库等方面,而不用去关心高层次的描述怎么转换为门级电路。综合工具在内部反复进行逻辑转换、优化,最终生成最优的门级电路。该过程如下所示。

结构解释

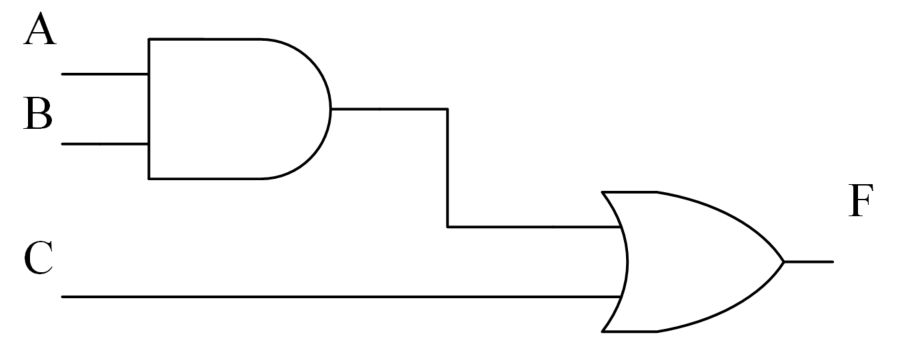

简单的赋值语句通常被综合为基本的逻辑门单元

assign F = (A & B) | C ;

上述代码通常会被综合为如下门级电路:

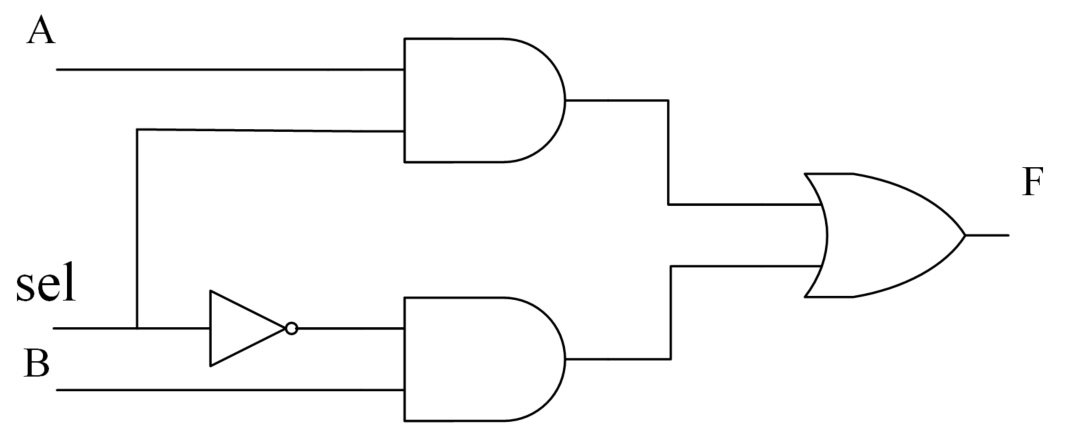

条件语句通常被综合为选择器

assign F = sel ? A : B ;

上述代码通常会被综合为如下门级电路:

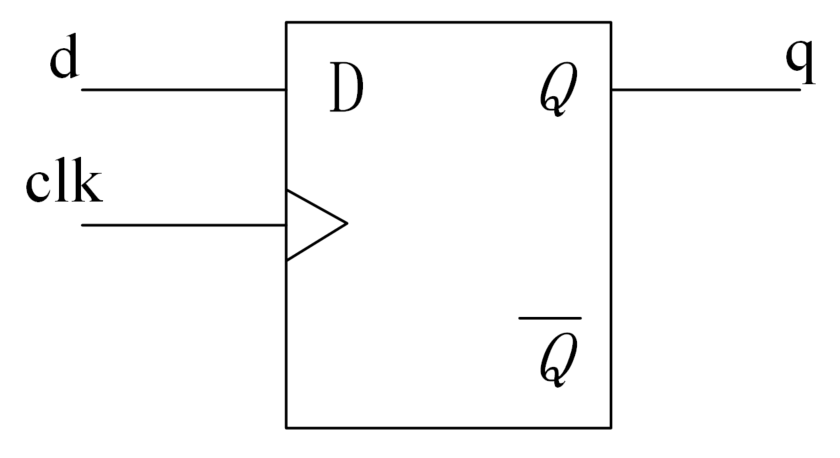

always 块中时钟触发的赋值语句通常被综合为触发器

always @(posedge clk) begin

q <= d ;

end

上述代码通常会被综合为如下电路:

再复杂的设计,综合之后,都会被转换为由各种单元库原件组成的门级网表。总之,逻辑综合可以狭隘的理解为,将 Verilog 设计转换为用优化的基本逻辑门单元、特殊的宏单元表示的过程。

综合流程

从高层次 RTL 描述到门级网表的详细综合过程如下图所示。

RTL 描述

用硬件描述语言(例如 Verilog)设计数字电路,并进行仿真保证逻辑功能的正确性。

翻译

RTL 描述会被综合工具转换为一个未经优化的中间表示。该过程读入 Verilog 描述的基本原语和操作,不考虑面积、时序、功耗等设计约束,仅完成简单的内部资源分配。

未优化的中间表示

翻译过程中产生的中间表示,数据格式由综合工具内部识别,用户无法也无需了解。

逻辑优化

优化设计逻辑,删除冗余逻辑。该过程往往会将 RTL 设计的一些变量删除,或重新命名,逻辑实现过程往往也会改变,以达到逻辑的最优化实现。该过程会产生优化的内部表示。

工艺映射和优化

此步骤之前,设计的描述过程是独立于目标工艺的。该步骤中,综合工具将使用工艺库(标准单元库)中提供的逻辑单元,实现设计的内部表示。即设计会被映射到目标工艺。实现过程中,还必须满足时序、面积和功耗的约束,执行一些局部的优化。

标准单元库

如之前所述,标准单元库对应工艺库,可以包含简单的与门、非门等基本逻辑门单元,也可以包含特殊的宏单元,例如乘法器、特殊的触发器等。

为了更好的映射与优化,每个逻辑单元,应当包含以下信息:

- 1、功能描述

- 2、版图面积

- 3、时序信息

- 4、 功耗信息

设计约束

设计约束一般包括时序、面积、功耗等方面的约束。三者之间往往存在制约关系。为了优化时序,可能需要增加硬件资源,导致电路面积增大,功耗增加。为了产生规模更小的电路,又必须在电路速度上进行妥协。数字电路设计时往往要综合各种因素进行取舍。

优化的门级表示

工艺映射与优化完成后,最终会生成由目标工艺库所描述的优化后的门级网表。如果该网表满足各种约束要求,则会被制作成最终的版图。否则还需要修改设计约束或优化 RTL 描述,以获得满足约束要求的门级网表结果。这个过程是反复的,直至最终网表满足要求。

点我分享笔记