3.5 Verilog 延迟反标注

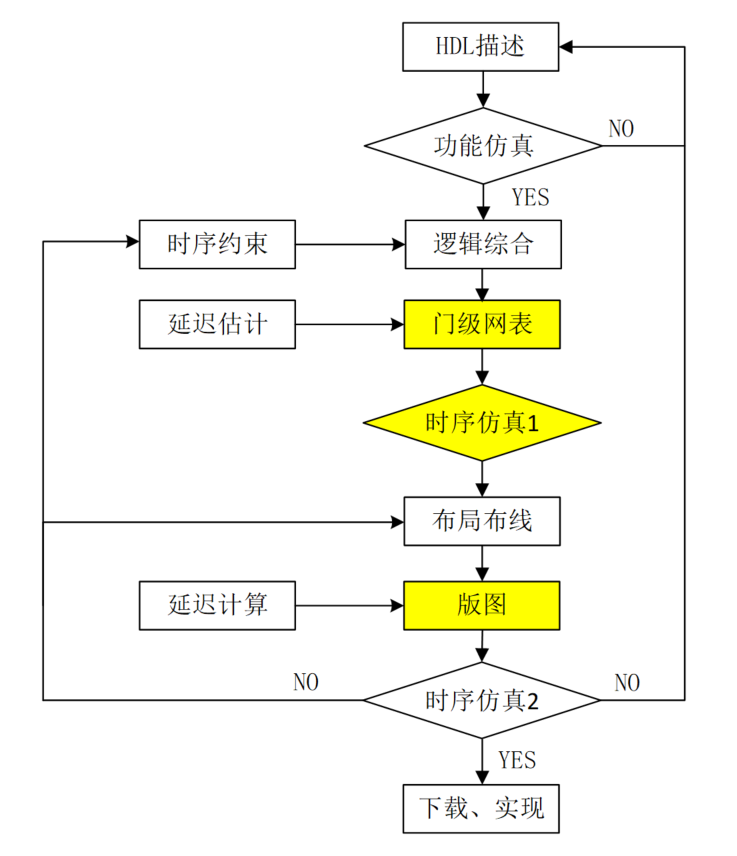

关键词: 延迟反标注, SDF 延迟反标注是设计者根据单元库工艺、门级网表、版图中的电容电阻等信息,借助数字设计工具将延迟信息标注到门级网...

3.4 Verilog 时序检查

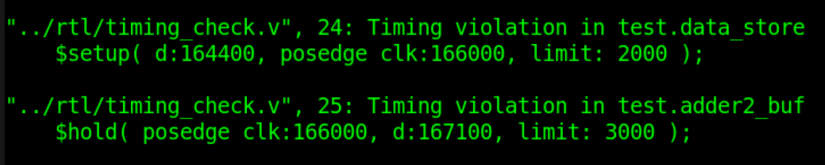

关键词: setup hold recovery removal width period 指定路径延迟,目的是让仿真的时序更加接近实际数字电路的时序。利用时序约束对数字设计...

3.3 Verilog 建立时间和保持时间

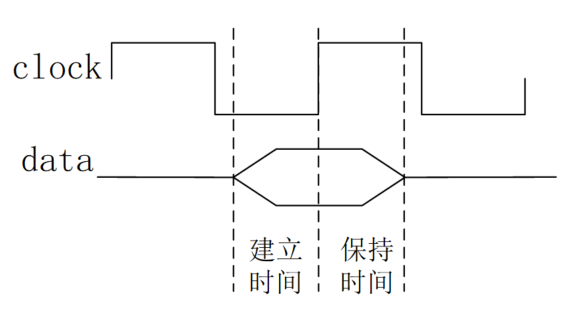

关键词: 建立时间, 保持时间 对于数字系统而言,建立时间(setup time)和保持时间(hold time)是数字电路时序的基础。数字电路系统的稳定...

3.2 Verilog specify 块语句

关键词: specify, 路径延迟 路径延迟用关键字 specify 和 endspecify 描述,关键字之间组成 specify 块语句。 specify 是模块中独立的一部...

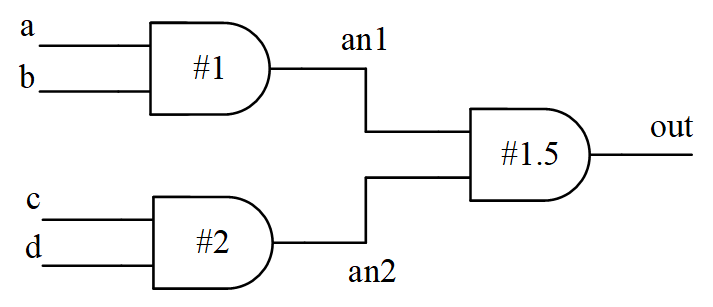

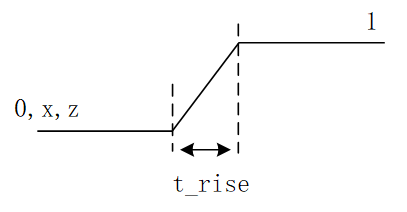

3.1 Verilog 延迟模型

关键词: 分布延迟, 集总延迟, 路径延迟 之前大部分仿真都是验证数字电路功能的正确性,信号传输都是理想的,没有延迟。但是实际逻辑元器件...

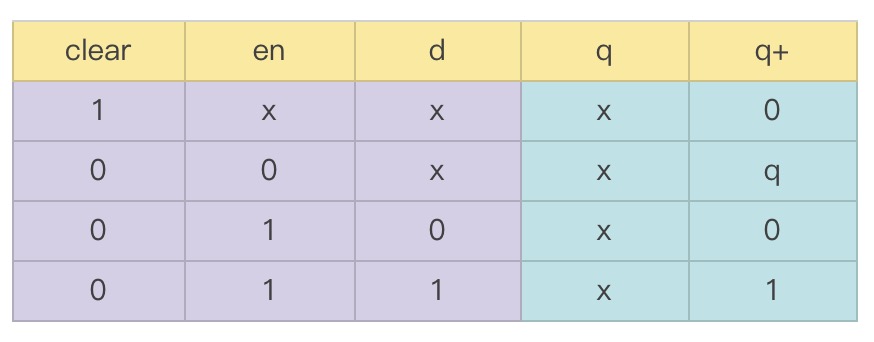

2.3 Verilog 时序逻辑 UDP

时序逻辑 UDP 与组合逻辑 UDP 在定义形式和行为功能上均有不同,主要区别如下: 1、时序逻辑 UDP 的输出端必须声明为 reg 型。 2、时序...

2.2 Verilog 组合逻辑 UDP

与非门实例 组合逻辑 UDP 中,状态表规定了不同的输入组合和相对应的输出值,没有指定的任意组合输出值为 x。 一个简单的与非门 UDP 可以表...

2.1 Verilog UDP 基础知识

门级建模中介绍的内置门单元,例如 and,or , nor 等,均属于 Verilog 自带的一整套标准原语,即通常所说的内置原语。 此外,Verilog 还为用...

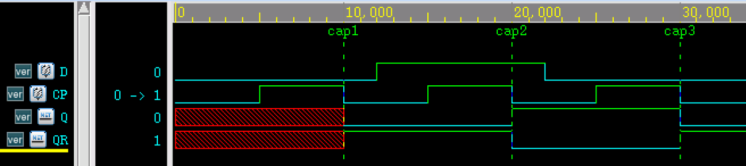

1.3 Verilog 门延迟

关键词: 门延迟, D 触发器 门延迟类型 前两节中所介绍的门级电路都是没有延迟的,实际门级电路都是有延迟的。 Verilog 中允许用户使用...

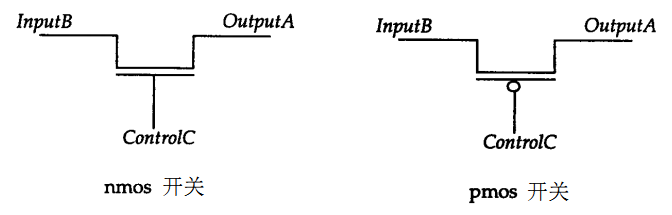

1.2 Verilog 开关级建模

关键词:MOS, CMOS, 双向开关, PAD 开关级建模是比门级建模更为低级抽象层次上的设计。在极少数情况下,设计者可能会选择使用晶体管作为设计...