7.4 Verilog CIC 滤波器设计

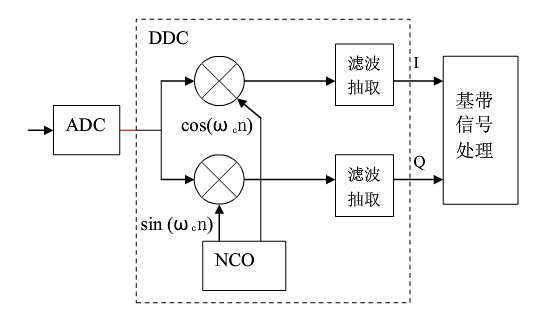

积分梳状滤波器(CIC,Cascaded Integrator Comb),一般用于数字下变频(DDC)和数字上变频(DUC)系统。CIC 滤波器结构简单,没有乘法器,只...

7.3 Verilog 串行 FIR 滤波器设计

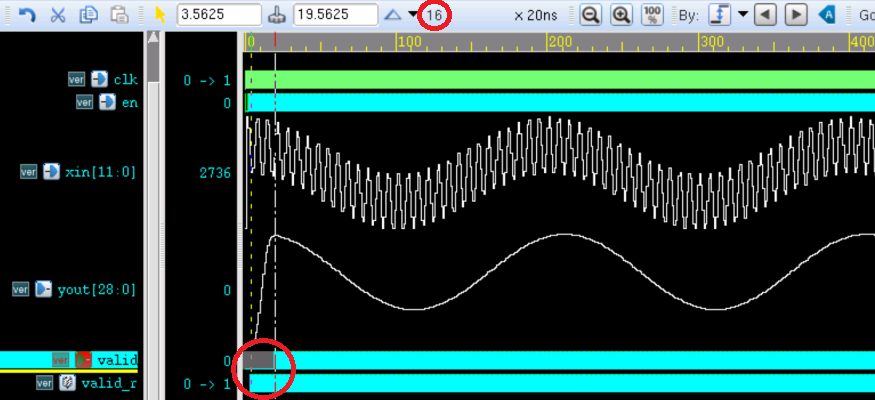

串行 FIR 滤波器设计 设计说明 设计参数不变,与并行 FIR 滤波器参数一致。即,输入频率为 7.5 MHz 和 250 KHz 的正弦波混合信号,经过 FIR ...

7.2 Verilog 并行 FIR 滤波器设计

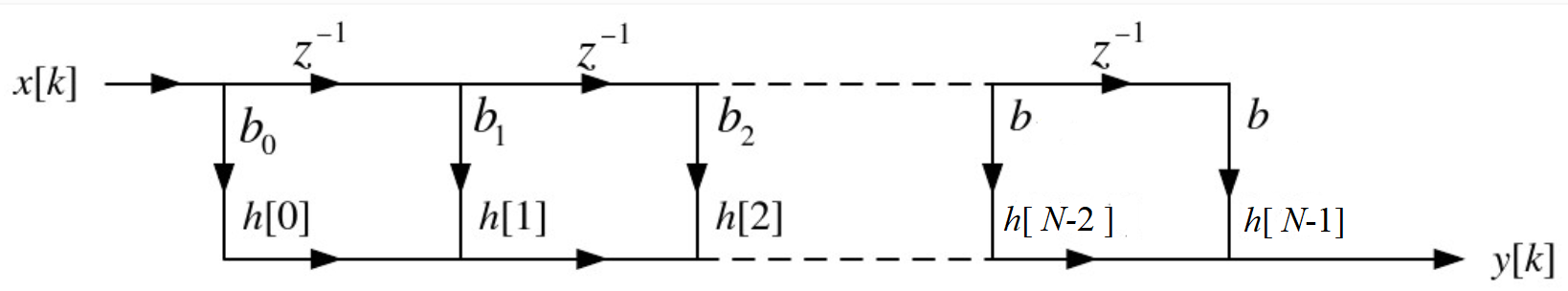

FIR(Finite Impulse Response)滤波器是一种有限长单位冲激响应滤波器,又称为非递归型滤波器。FIR 滤波器具有严格的线性相频特性,同时其单...

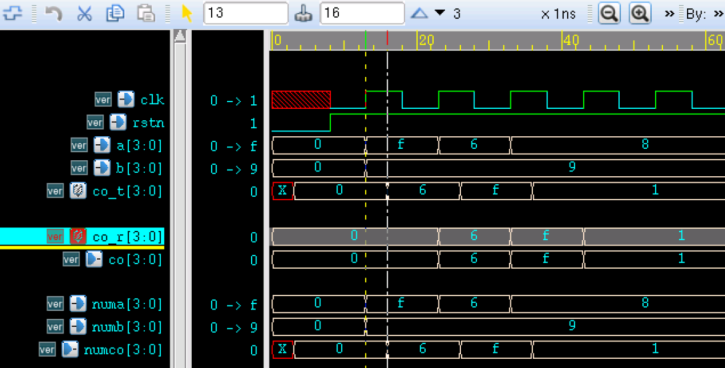

7.1 Verilog 除法器设计

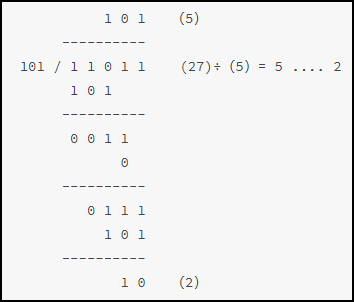

除法器原理(定点) 和十进制除法类似,计算 27 除以 5 的过程如下所示: 除法运算过程如下: (1) 取被除数的高几位数据,位宽和除数...

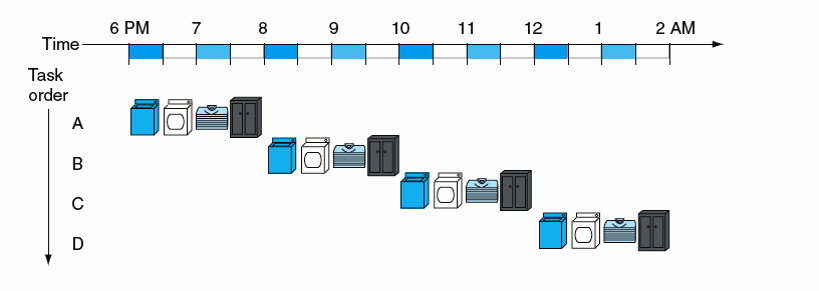

6.7 Verilog 流水线

关键词:流水线,乘法器硬件描述语言的一个突出优点就是指令执行的并行性。多条语句能够在相同时钟周期内并行处理多个信号数据。 但是当数据...

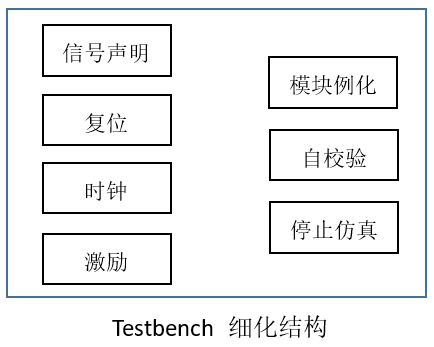

6.6 Verilog 仿真激励

关键词:testbench,仿真,文件读写 Verilog 代码设计完成后,还需要进行重要的步骤,即逻辑功能仿真。仿真激励文件称之为 testbench,放在各...

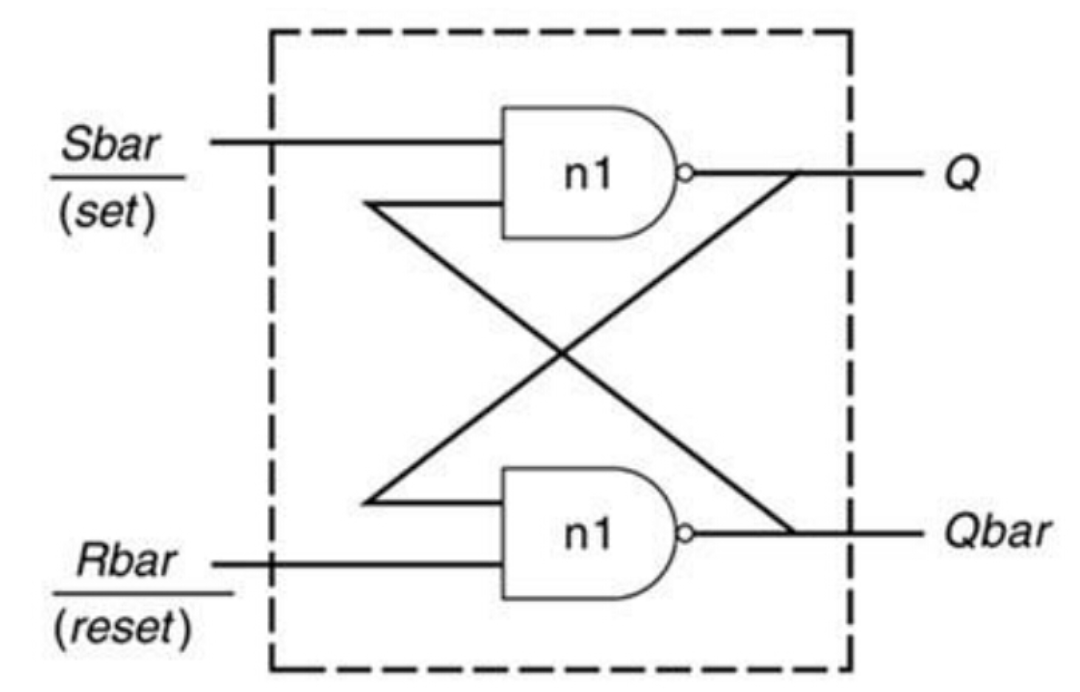

6.5 Verilog 避免 Latch

关键词:触发器,锁存器 Latch 的含义 锁存器(Latch),是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值。仅...

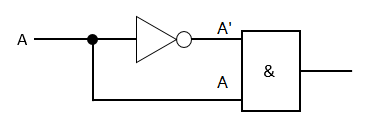

6.4 Verilog 竞争与冒险

关键字:竞争,冒险,书写规范 产生原因 数字电路中,信号传输与状态变换时都会有一定的延时。 在组合逻辑电路中,不同路径的输入信号变化...

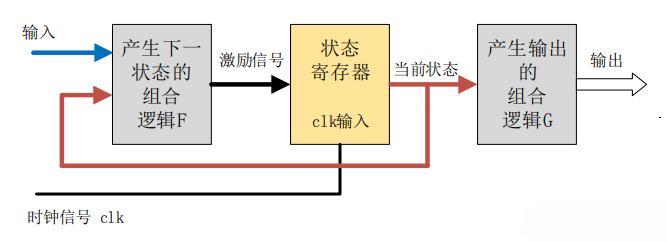

6.3 Verilog 状态机

关键词:状态机,售卖机 有限状态机(Finite-State Machine,FSM),简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数...

6.2 Verilog 任务

关键词:任务 任务与函数的区别 和函数一样,任务(task)可以用来描述共同的代码段,并在模块内任意位置被调用,让代码更加的直观易读。函...