1.0 Hadoop 教程

Hadoop 是一个开源的分布式计算和存储框架,由 Apache 基金会开发和维护。 Hadoop 为庞大的计算机集群提供可靠的、可伸缩的应用层计算和存储...

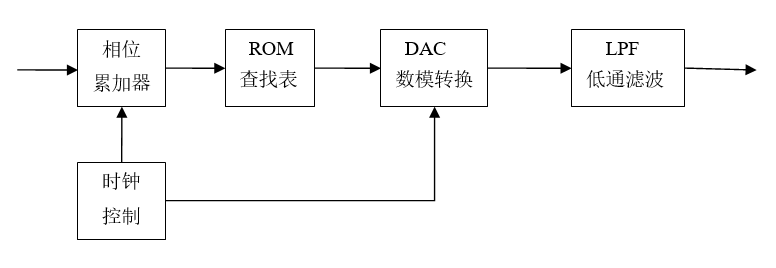

7.6 Verilog DDS 设计

DDS 原理 DDS(直接频率合成)技术是根据奈奎斯特抽样定理及数字处理技术,把一系列的模拟信号进行不失真的抽样,将得到的数字信号存储在存储...

8.1 Verilog 数值转换

本节主要对有符号数的十进制与二进制表示以及一些数值变换进行简单的总结。 定义一个宽度为 DW 的二进制补码格式的数据 dbin ,其表示的有符...

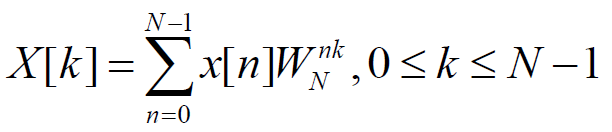

7.5 Verilog FFT 设计

FFT(Fast Fourier Transform),快速傅立叶变换,是一种 DFT(离散傅里叶变换)的高效算法。在以时频变换分析为基础的数字处理方法中,有着不...

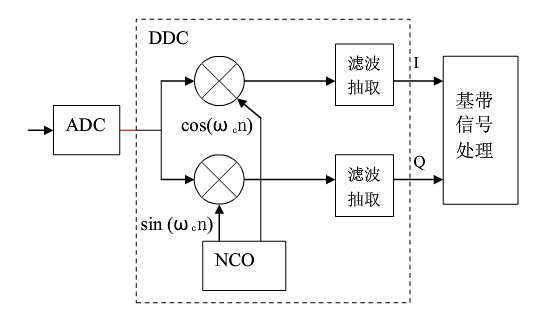

7.4 Verilog CIC 滤波器设计

积分梳状滤波器(CIC,Cascaded Integrator Comb),一般用于数字下变频(DDC)和数字上变频(DUC)系统。CIC 滤波器结构简单,没有乘法器,只...

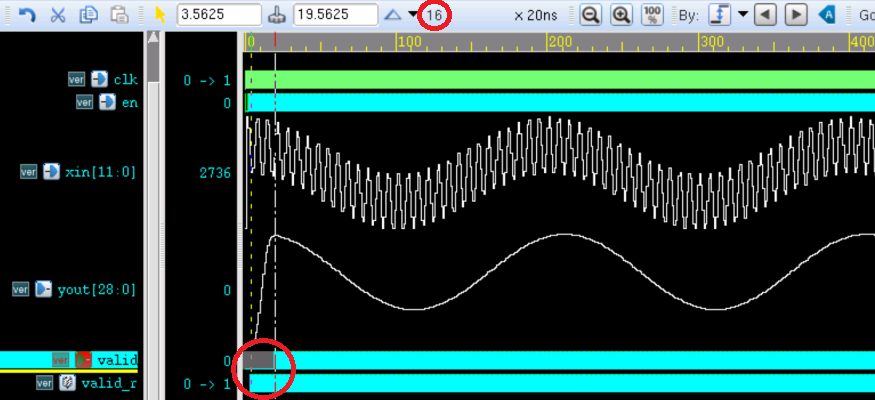

7.3 Verilog 串行 FIR 滤波器设计

串行 FIR 滤波器设计 设计说明 设计参数不变,与并行 FIR 滤波器参数一致。即,输入频率为 7.5 MHz 和 250 KHz 的正弦波混合信号,经过 FIR ...

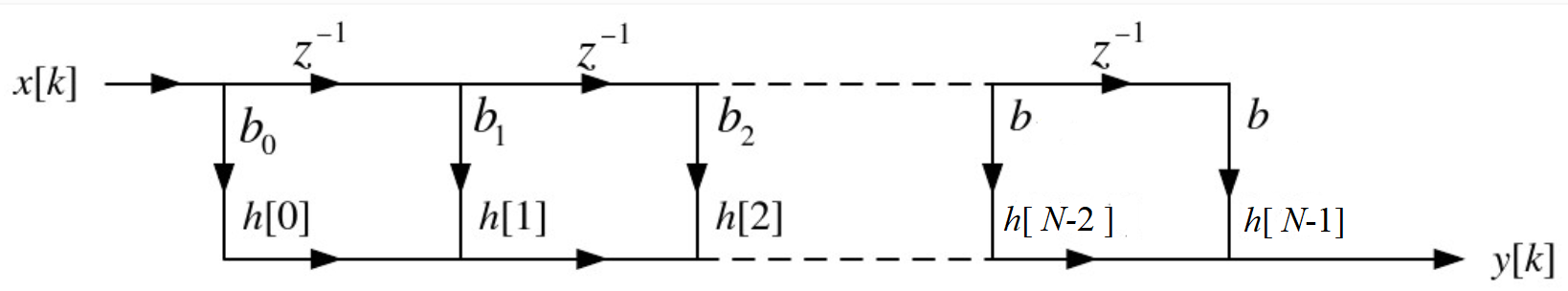

7.2 Verilog 并行 FIR 滤波器设计

FIR(Finite Impulse Response)滤波器是一种有限长单位冲激响应滤波器,又称为非递归型滤波器。FIR 滤波器具有严格的线性相频特性,同时其单...

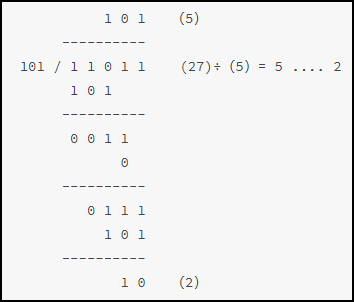

7.1 Verilog 除法器设计

除法器原理(定点) 和十进制除法类似,计算 27 除以 5 的过程如下所示: 除法运算过程如下: (1) 取被除数的高几位数据,位宽和除数...

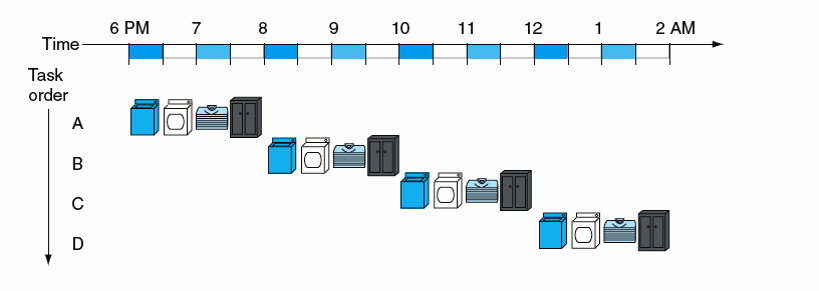

6.7 Verilog 流水线

关键词:流水线,乘法器硬件描述语言的一个突出优点就是指令执行的并行性。多条语句能够在相同时钟周期内并行处理多个信号数据。 但是当数据...

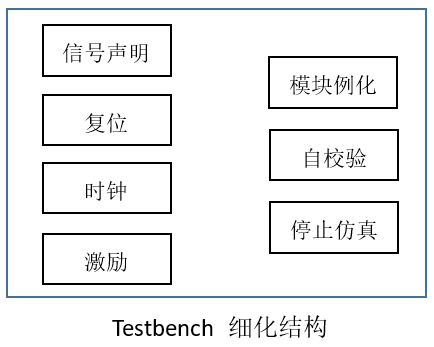

6.6 Verilog 仿真激励

关键词:testbench,仿真,文件读写 Verilog 代码设计完成后,还需要进行重要的步骤,即逻辑功能仿真。仿真激励文件称之为 testbench,放在各...